# int 82375EB/82375SB PCI-EISA BRIDGE (PCEB)

- Provides the Bridge Between the PCI Local Bus and EISA Bus

- 100% PCI and EISA Compatible

- PCI and EISA Master/Slave Interface Directly Drives 10 PCI Loads and 8 **EISA Slots**

- Supports PCI from 25 to 33 MHz

- Data Buffers Improve Performance - Four 32-bit PCI-to-EISA Posted Write Buffers

- Four 16-byte EISA-to-PCI Read/Write Line Buffers

- EISA-to-PCI Read Prefetch

- EISA-to-PCI and PCI-to-EISA Write Posting

- Data Buffer Management Ensures Data Coherency

- Flush Posted Write Buffers

- Flush or Invalidate Line Buffers

- System-Wide Data Buffer Coherency Control

- Burst Transfers on both the PCI and **EISA Buses**

- 32-Bit Data Paths

- Integrated EISA Data Swap Buffers

- Arbitration for PCI Devices

- Supports Six PCI Masters

- Fixed, Rotating, or a Combination of the Two

- Supports External PCI Arbiter and Arbiter Cascading

- PCI and EISA Address Decoding and Mapping

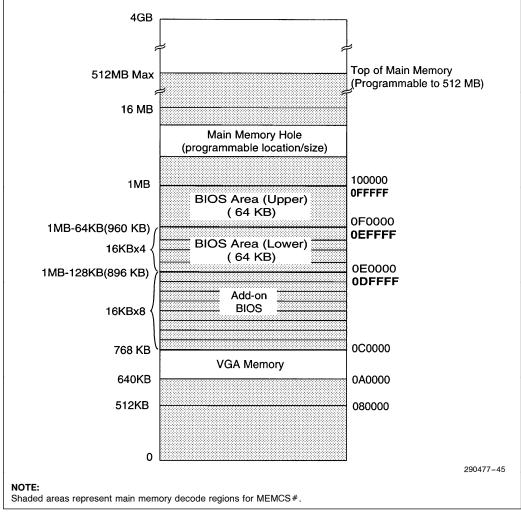

- Positive Decode of Main Memory Areas (MEMCS # Generation)

- Four Programmable PCI Memory **Space Regions**

- Four Programmable PCI I/O Space Regions

- Programmable Main Memory Address Decoding

- Main Memory Sizes up to 512 MBytes

- Access Attributes for 15 Memory Segments in First 1 MByte of Main Memory

- Programmable Main Memory Hole

- Integrated 16-bit BIOS Timer

- Only Available as Part of a Supported Kit

The 82375EB/SB PCI-EISA Bridge (PCEB) provides the master/slave functions on both the PCI Local Bus and the EISA Bus. Functioning as a bridge between the PCI and EISA buses, the PCEB provides the address and data paths, bus controls, and bus protocol translation for PCI-to-EISA and EISA-to-PCI transfers. Extensive data buffering in both directions increases system performance by maximizing PCI and EISA Bus efficiency and allowing concurrency on the two buses. The PCEB's buffer management mechanism ensures data coherency. The PCEB integrates central bus control functions including a programmable bus arbiter for the PCI Bus and EISA data swap buffers for the EISA Bus. Integrated system functions include PCI parity generation, system error reporting, and programmable PCI and EISA memory and I/O address space mapping and decoding. The PCEB also contains a BIOS Timer that can be used to implement timing loops. The PCEB is intended to be used with the EISA System Component (ESC) to provide an EISA I/O subsystem interface.

This document describes both the 82375EB and 82375SB components. Unshaded areas describe the 82375EB. Shaded areas, like this one, describe the 82375SB operations that differ from the 82375EB.

\*Other brands and names are the property of their respective owners. Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata. COPYRIGHT © INTEL CORPORATION, 1996 March 1996 Order Number: 290477-004

# intel

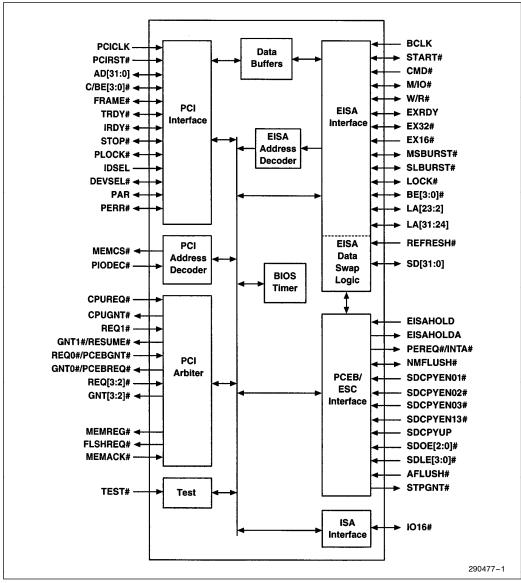

#### PCEB Simplified Block Diagram

# 82375EB/82375SB PCI-EISA BRIDGE (PCEB)

| <b>CONTENTS</b> PAGE                                                                                              |

|-------------------------------------------------------------------------------------------------------------------|

| 1.0 ARCHITECTURAL OVERVIEW         8           1.1 PCEB Overview         10           1.2 ESC Overview         12 |

| 2.0 SIGNAL DESCRIPTION                                                                                            |

| 2.1 PCI Bus Interface Signals       15         2.2 PCI Arbiter Signals       18                                   |

| 2.3 Address Decoder Signals                                                                                       |

| 2.4 EISA Interface Signals                                                                                        |

| 2.5 ISA Interface Signals                                                                                         |

| 2.6 PCEB/ESC Interface Signals                                                                                    |

| 2.7 Test Signal                                                                                                   |

| 3.0 REGISTER DESCRIPTION                                                                                          |

| 3.1 Configuration Registers                                                                                       |

| 3.1.1 VID—VENDOR IDENTIFICATION REGISTER                                                                          |

| 3.1.2 DID—DEVICE IDENTIFICATION REGISTER                                                                          |

| 3.1.3 PCICMD—PCI COMMAND REGISTER                                                                                 |

| 3.1.4 PCISTS—PCI STATUS REGISTER                                                                                  |

| 3.1.5 RID—REVISION IDENTIFICATION REGISTER                                                                        |

| 3.1.7 PCICON—PCI CONTROL REGISTER                                                                                 |

| 3.1.8 ARBCON—PCI ARBITER CONTROL REGISTER                                                                         |

| 3.1.9 ARBPRI—PCI ARBITER PRIORITY CONTROL REGISTER                                                                |

| 3.1.10 ARBPRIX—PCI ARBITER PRIORITY CONTROL EXTENSION REGISTER                                                    |

| 3.1.11 MCSCON—MEMCS # CONTROL REGISTER                                                                            |

| 3.1.12 MCSBOH—MEMCS # BOTTOM OF HOLE REGISTER                                                                     |

| 3.1.13 MCSTOH—MEMCS# TOP OF HOLE REGISTER                                                                         |

| 3.1.14 MCSTOM—MEMCS # TOP OF MEMORY REGISTER                                                                      |

| 3.1.15 EADC1—EISA ADDRESS DECODE CONTROL 1 REGISTER                                                               |

| 3.1.16 IORT—ISA I/O RECOVERY TIMER REGISTER                                                                       |

| 3.1.17 MAR1—MEMCS# ATTRIBUTE REGISTER #1                                                                          |

| 3.1.18 MAR2—MEMCS# ATTRIBUTE REGISTER #2                                                                          |

| 3.1.19 MAR3—MEMCS# ATTRIBUTE REGISTER #3                                                                          |

| 3.1.20 PDCON—PCI DECODE CONTROL REGISTER                                                                          |

| 0.1.21 EADOZ EIGAADDITEOG DEGODE GONTITOE EATENOION THEGIOTETT                                                    |

| CONTENTS                                                        | PAGE |

|-----------------------------------------------------------------|------|

| 3.1.22 EPMRA—EISA-TO-PCI MEMORY REGION ATTRIBUTES REGISTER      |      |

| 3.1.23 MEMREGN[4:1]—EISA-TO-PCI MEMORY REGION ADDRESS REGISTERS |      |

| 3.1.24 IOREGN[4:1]—EISA-TO-PCI I/O REGION ADDRESS REGISTERS     |      |

| 3.1.25 BTMR—BIOS TIMER BASE ADDRESS REGISTER                    |      |

| 3.1.26 ELTCR—EISA LATENCY TIMER CONTROL REGISTER                |      |

| 3.2 I/O Registers                                               |      |

| 3.2.1 BIOSTM—BIOS TIMER REGISTER                                |      |

| 4.0 ADDRESS DECODING                                            | 48   |

| 4.1 PCI Cycle Address Decoding                                  |      |

| 4.1.1 MEMORY SPACE ADDRESS DECODING                             |      |

| 4.1.1.1 Main Memory Decoding (MEMCS#)                           |      |

| 4.1.1.2 BIOS Memory Space                                       |      |

| 4.1.1.3 Subtractively And Negatively Decoded Cycles To EISA     |      |

| 4.1.2 PCEB CONFIGURATION REGISTERS                              |      |

| 4.1.3 PCEB I/O REGISTERS                                        |      |

| 4.1.4 POSITIVELY DECODED COMPATIBILITY I/O REGISTERS            | 56   |

| 4.1.4.1 ESC Resident PIC Registers                              | 57   |

| 4.1.4.2 EISA Resident IDE Registers                             |      |

| 4.2. EISA Cycle Address Decoding                                | 58   |

| 4.2.1 POSITIVELY DECODED MEMORY CYCLES TO MAIN MEMORY           | 58   |

| 4.2.2 PROGRAMMABLE EISA-TO-PCI MEMORY ADDRESS REGIONS           | 61   |

| 4.2.3 PROGRAMMABLE EISA-TO-PCI I/O ADDRESS REGIONS              | 61   |

| 4.2.4 EXTERNAL EISA-TO-PCI I/O ADDRESS DECODER                  | 62   |

| 4.3 Palette DAC Snoop Mechanism                                 | 62   |

| 5.0 PCI INTERFACE                                               | 62   |

| 5.1 PCI Bus Transactions                                        | 63   |

| 5.1.1 PCI COMMAND SET                                           | 63   |

| 5.1.2 PCI CYCLE DESCRIPTIONS                                    | 64   |

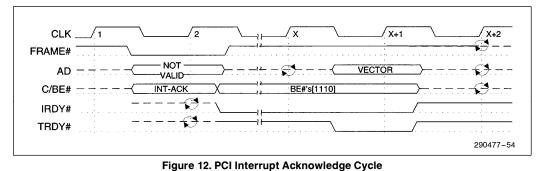

| 5.1.2.1 Interrupt Acknowledge                                   | 64   |

| 5.1.2.2 Special Cycle                                           | 65   |

| 5.1.2.3 I/O Read                                                | 65   |

| 5.1.2.4 I/O Write                                               | 65   |

| 5.1.2.5 Memory Read                                             | 66   |

| 5.1.2.6 Memory Write                                            | 67   |

| 5.1.2.7 Configuration Read, Configuration Write                 | 67   |

| 5.1.2.8 Memory Read Multiple                                    | 68   |

|                                                                           | PAGE |

|---------------------------------------------------------------------------|------|

| 5.1.2.9 Memory Read Line                                                  |      |

| 5.1.2.10 Memory Write And Invalidate                                      |      |

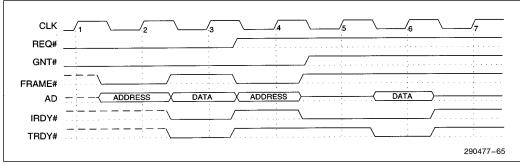

| 5.1.3 PCI TRANSFER BASICS                                                 |      |

| 5.1.3.1 Turn-Around-Cycle Definition                                      |      |

| 5.1.3.2 Idle Cycle Definition                                             |      |

| 5.1.4 BASIC READ                                                          |      |

| 5.1.5 BASIC WRITE                                                         |      |

| 5.1.6 CONFIGURATION CYCLES                                                |      |

| 5.1.7 INTERRUPT ACKNOWLEDGE CYCLE                                         |      |

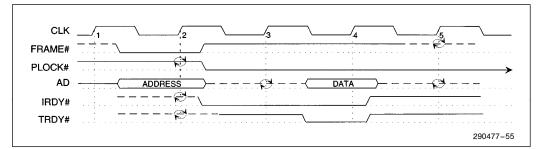

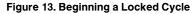

| 5.1.8 EXCLUSIVE ACCESS                                                    |      |

| 5.1.9 DEVICE SELECTION                                                    |      |

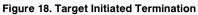

| 5.1.10 TRANSACTION TERMINATION                                            | 78   |

| 5.1.10.1 Master Initiated Termination                                     | 78   |

| 5.1.10.2 Target Initiated Termination                                     | 79   |

| 5.1.10.3 PCEB Target Termination Conditions                               | 81   |

| 5.1.10.4 PCEB Master Termination Conditions                               | 81   |

| 5.1.10.5 PCEB Responses/Results Of Termination                            | 81   |

| 5.1.11 PCI DATA TRANSFERS WITH SPECIFIC BYTE ENABLE COMBINATIONS $\ldots$ | 82   |

| 5.2 PCI Bus Latency                                                       | 82   |

| 5.2.1 MASTER LATENCY TIMER (MLT)                                          | 82   |

| 5.2.2 INCREMENTAL LATENCY MECHANISM                                       | 83   |

| 5.3 PCI Bus Parity Support And Error Reporting                            | 83   |

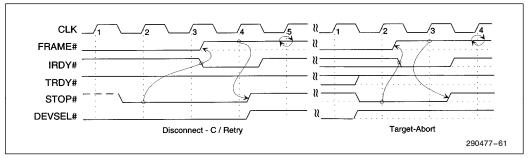

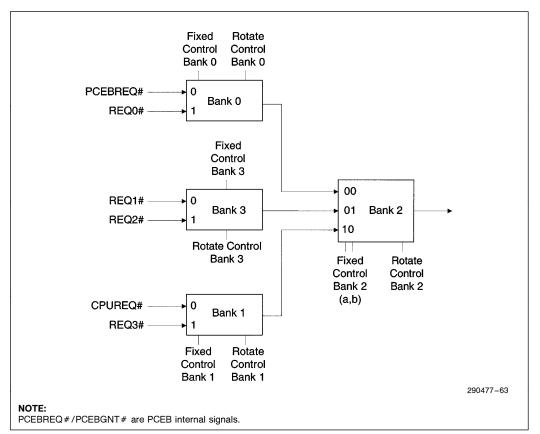

| 5.3.1 PARITY GENERATION AND CHECKING                                      | 83   |

| 5.3.1.1 Address Phase                                                     | 84   |

| 5.3.1.2 Data Phase                                                        | 84   |

| 5.3.2 PARITY ERROR—PERR # SIGNAL                                          | 84   |

| 5.3.3 SYSTEM ERRORS                                                       | 84   |

| 5.4 PCI Bus Arbitration                                                   | 85   |

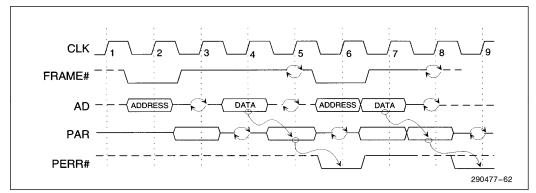

| 5.4.1 PCI ARBITER CONFIGURATION                                           | 85   |

| 5.4.1.1 Fixed Priority Mode                                               | 87   |

| 5.4.1.2 Rotating Priority Mode                                            | 89   |

| 5.4.1.3 Mixed Priority Mode                                               | 89   |

| 5.4.1.4 Locking Masters                                                   |      |

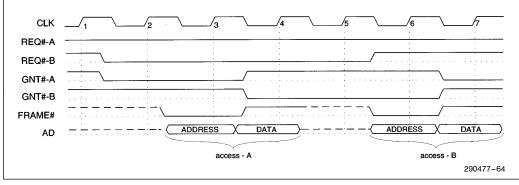

| 5.4.2 ARBITRATION SIGNALING PROTOCOL                                      |      |

| 5.4.2.1 REQ# and GNT# Rules                                               | 90   |

| 5.4.2.2 Back-to-Back Transactions                                         |      |

| CONTENTS                                                   | PAGE |

|------------------------------------------------------------|------|

| 5.4.3 RETRY THRASHING RESOLVE                              | 91   |

| 5.4.3.1 Resume Function                                    |      |

| 5.4.3.2 Master Retry Timer                                 | 92   |

| 5.4.4 BUS LOCK MODE                                        | 92   |

| 5.4.5 MEMREQ#, FLSHREQ#, AND MEMACK# PROTOCOL              | 92   |

| 5.4.5.1 Flushing System Posted Write Buffers               | 93   |

| 5.4.5.2 Guaranteed Access Time Mode                        |      |

| 5.4.5.3 Interrupt Synchronization-Buffer Flushing          |      |

| 5.4.6 BUS PARKING                                          |      |

| 5.4.7 PCI ARBITRATION AND PCEB/ESC EISA OWNERSHIP EXCHANGE |      |

| 5.4.7.1 GAT Mode and PEREQ# Signaling                      |      |

| 5.4.7.2 PCI Retry and EISA Latency Timer (ELT) Mechanism   |      |

| 6.0 DATA BUFFERING                                         |      |

| 6.1 Line Buffers                                           |      |

| 6.1.1 WRITE STATE                                          |      |

| 6.1.2 READ STATE                                           |      |

| 6.2 Buffer Management Summary                              | 100  |

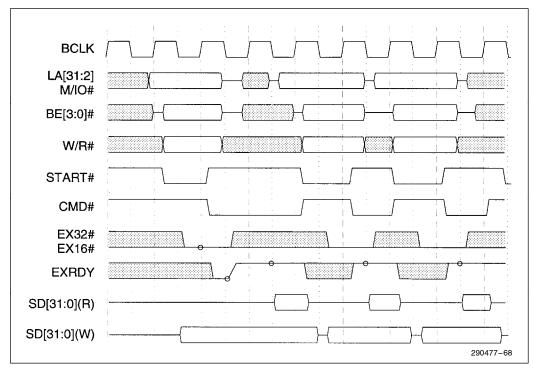

| 7.0 EISA INTERFACE                                         | 101  |

| 7.1 PCEB As An EISA Master                                 |      |

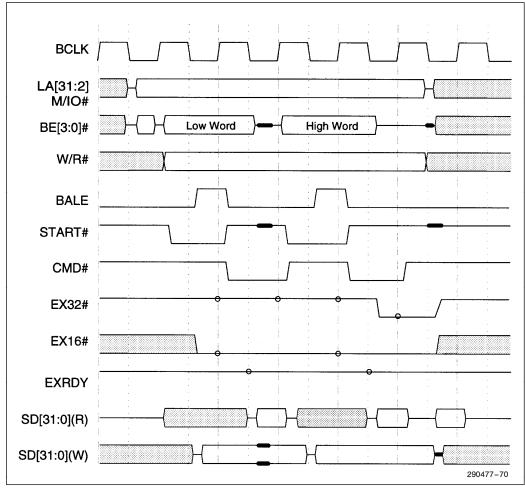

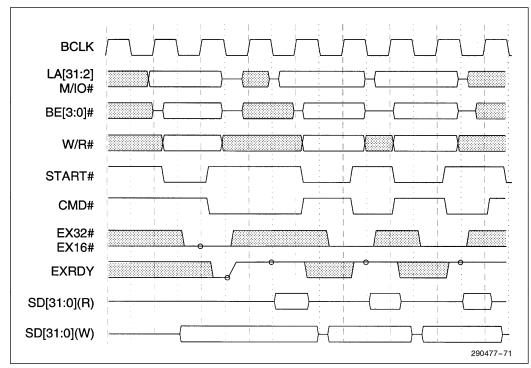

| 7.1.1 STANDARD EISA MEMORY AND I/O READ/WRITE CYCLES       |      |

| 7.1.2 EISA BACK-OFF CYCLE                                  |      |

| 7.2 PCEB As An EISA Slave                                  |      |

| 7.2.1 EISA MEMORY AND I/O READ/WRITE CYCLES                |      |

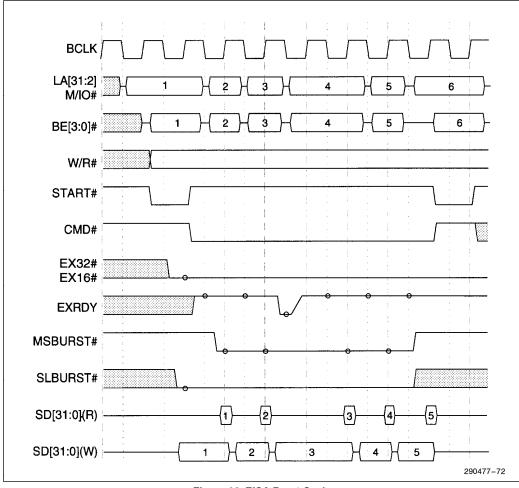

| 7.2.2 EISA MEMORY BURST CYCLES                             | 107  |

| 7.3 I/O Recovery                                           | 108  |

| 8.0 EISA DATA SWAP BUFFERS                                 |      |

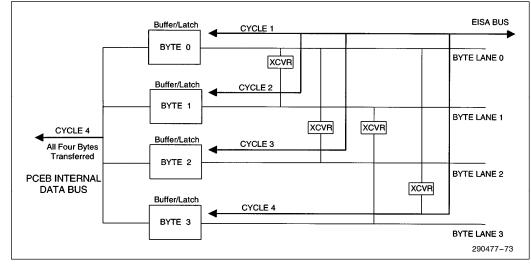

| 8.1 Data Assembly And Disassembly                          |      |

| 8.2 The Copy Operation (Up Or Down)                        |      |

| 8.3 The Re-Drive Operation                                 |      |

| 9.0 BIOS TIMER                                             | 11/  |

| 9.1 Bios Timer Operations                                  |      |

| L                                                          |      |

# **CONTENTS**

# PAGE 10.3 Power Management (82375SB) ..... 117

| 12.2 Package Characteristics | 127 |

|------------------------------|-----|

| 13.0 TESTABILITY             | 128 |

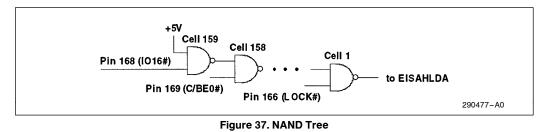

| 13.1 NAND Tree               | 128 |

# 7

# **1.0 ARCHITECTURAL OVERVIEW**

The PCI-EISA bridge chip set provides an I/O subsystem core for the next generation of high-performance personal computers (e.g., those based on the Intel486<sup>TM</sup> or Pentium<sup>®</sup> processors). System designers can take advantage of the power of the PCI local bus while maintaining access to the large base of EISA and ISA expansion cards, and corresponding software applications. Extensive buffering and buffer management within the PCI-EISA bridge ensures maximum efficiency in both bus environments.

The chip set consists of two components—the 82375EB PCI-EISA Bridge (PCEB) and the 82374EB EISA System Component (ESC). These components work in tandem to provide an EISA I/O subsystem interface for personal computer platforms based on the PCI standard. This section provides an overview of the PCI and EISA Bus hierarchy followed by an overview of the PCEB and ESC components.

#### **Bus Hierarchy—Concurrent Operations**

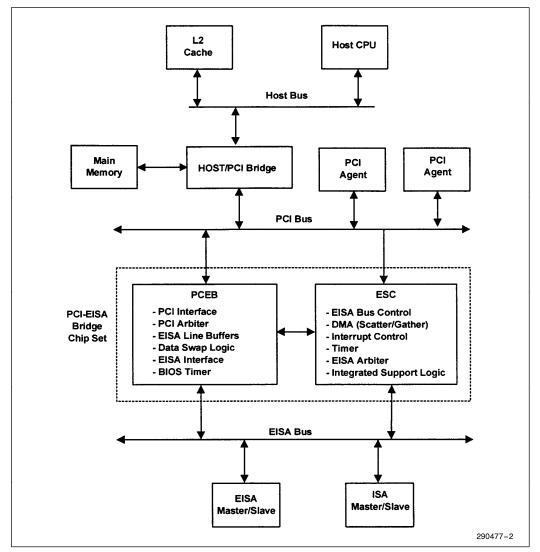

Figure 1 shows a block diagram of a typical system using the PCI-EISA Bridge chip set. The system contains three levels of buses structured in the following hierarchy:

- Host Bus as the execution bus

- PCI Bus as a primary I/O bus

- EISA Bus as a secondary I/O bus

#### PCI Bus

The PCI Bus has been defined to address the growing industry needs for a standardized *local bus* that is not directly dependent on the speed and the size of the processor bus. New generations of personal computer system software such as Windows™ and Win-NT™ with sophisticated graphical interfaces, multi-tasking and multi-threading bring new requirements that traditional PC I/O architectures can not satisfy. In addition to the higher bandwidth, reliability and robustness of the I/O subsystem are becoming increasingly important. The PCI environment addresses these needs and provides an upgrade path for the future. PCI features include:

- Processor independent

- · Multiplexed, burst mode operation

- Synchronous up to 33 MHz

- 120 MByte/sec usable throughput (132 MByte/sec peak) for 32-bit data path

- 240 MByte/sec usable throughput (264 MByte/sec peak) for 64-bit data path

- Optional 64-bit data path with operations that are transparent with the 32-bit data path

- · Low latency random access (60 ns write access latency to slaves from a master parked on the bus)

- · Capable of full concurrency with processor/memory subsystem

- · Full multi-master capability allowing any PCI master peer-to-peer access to any PCI slave

- Hidden (overlapped) central arbitration

- · Low pin count for cost effective component packaging (multiplexed address/data)

- Address and data parity

- Three physical address spaces: memory, I/O, and configuration

- · Comprehensive support for autoconfiguration through a defined set of standard configuration functions

Figure 1. PCI-EISA System Diagram

System partitioning shown in Figure 1 illustrates how the PCI can be used as a common interface between different portions of a system platform that are typically supplied by the chip set vendor. These portions are the Host/PCI Bridge (including a main memory DRAM controller and an optional secondary cache controller) and the PCI-EISA Bridge. Thus, the PCI allows a system I/O core design to be decoupled from the processor/

memory treadmill, enabling the I/O core to provide maximum benefit over multiple generations of processor/ memory technology. For this reason, the PCI-EISA Bridge can be used with different processors (i.e. derivatives of the Intel486 CPU or the new generation processors, such as the Pentium processor.) Regardless of the new requirements imposed on the processor side of the Host/PCI Bridge (e.g. 64-bit data path, 3.3V interface, etc.) the PCI side remains unchanged. This standard PCI environment allows reusability, not only of the rest of the platform chip set (i.e. PCI-EISA Bridge), but also of all other I/O functions interfaced at the PCI level. These functions typically include graphics, SCSI, and LAN.

#### **EISA Bus**

The EISA bus in the system shown in the Figure 1 represents a second level I/O bus. It allows personal computer platforms built around the PCI as a primary I/O bus to leverage the large EISA/ISA product base. Combinations of PCI and EISA buses, both of which can be used to provide expansion functions, will satisfy even the most demanding applications.

Along with compatibility for 16-bit and 8-bit ISA hardware and software, the EISA bus provides the following key features:

- 32-bit addressing and 32-bit data path

- 33 MByte/sec bus bandwidth

- Multiple bus master support through efficient arbitration

- Support for autoconfiguration

#### Integrated Bus Central Control Functions

The PCI-EISA Bridge chip set integrates central bus functions on both the PCI and EISA Buses. For PCI, the functions include PCI bus arbitration and the default bus driver. For the EISA Bus, central functions include the EISA Bus controller and EISA arbiter that are integrated in the ESC and EISA data swap buffers that are integrated in the PCEB.

#### Integrated System Functions

The PCI-EISA Bridge chip set integrates system functions including PCI parity and system error reporting, buffer management, PCI and EISA memory and I/O address space mapping and decoding. For maximum flexibility, all of these functions are programmable allowing for variety of optional features.

## 1.1 PCEB Overview

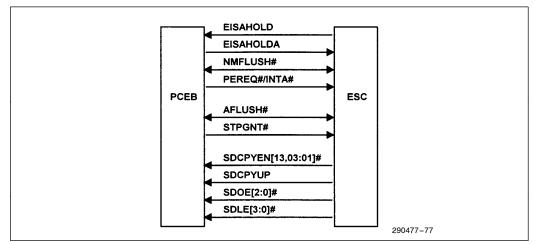

The PCEB and ESC form a PCI-EISA Bridge chip set. The PCEB/ESC interface provides the inter-chip communications between these two devices. The major functions provided by the PCEB are described in this section.

#### PCI Bus Interface

The PCEB can be either a master or slave on the PCI Bus and supports bus frequencies from 25-to-33 MHz. The PCEB becomes a slave when it positively decodes a PCI cycle. The PCEB also becomes a slave for unclaimed cycles on the PCI Bus. These unclaimed cycles are subtractively decoded by the PCEB and forwarded to the EISA Bus. As a slave, the PCEB supports single cycle transfers for memory, I/O, and configuration operations.

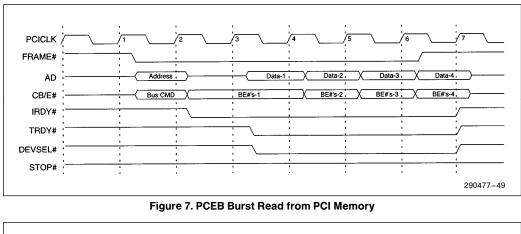

For EISA-initiated transfers to the PCI Bus, the PCEB is a PCI master. The PCEB permits EISA devices to access either PCI memory or I/O. While all PCI I/O transfers are single cycle, PCI memory cycles can be either single cycle or burst, depending on the status of the PCEB's Line Buffers. During EISA reads of PCI memory, the PCEB uses a burst read cycle of four Dwords to prefetch data into a Line Buffer. During EISA-to-PCI memory writes, the PCEB uses PCI burst cycles to flush the Line Buffers. The PCEB contains a programmable Master Latency Timer that provides the PCEB with a guaranteed time slice on the PCI Bus, after which it surrenders the bus.

As a master on the PCI Bus, the PCEB generates address and command signals (C/BE[3:0] #), address parity for read and write cycles, and data parity for write cycles. As a slave, the PCEB generates data parity for read cycles. Parity checking is not supported.

The PCEB, as a resource, can be locked by any PCI master. In the context of locked cycles, the entire PCEB subsystem (including the EISA Bus) is considered a single resource.

#### **PCI Bus Arbitration**

The PCI arbiter supports six PCI masters—the Host/PCI bridge, PCEB, and four other PCI masters. The arbiter can be programmed for twelve fixed priority schemes, a rotating scheme, or a combination of the fixed and rotating schemes. The arbiter can be programmed for bus parking that permits the Host/PCI Bridge default access to the PCI Bus when no other device is requesting service. The arbiter also contains an efficient PCI retry mechanism to minimize PCI Bus thrashing when the PCEB generates a retry.

#### **EISA Bus Interface**

The PCEB contains a fully EISA-compatible master and slave interface. The PCEB directly drives eight EISA slots without external data or address buffering. The PCEB is only a master or slave on the EISA Bus for transfers between the EISA Bus and PCI Bus. For transfers contained to the EISA Bus, the PCEB is never a master or slave. However, the data swap buffers contained in the PCEB are involved in these transfers, if data size translation is needed. The PCEB also provides support for I/O recovery.

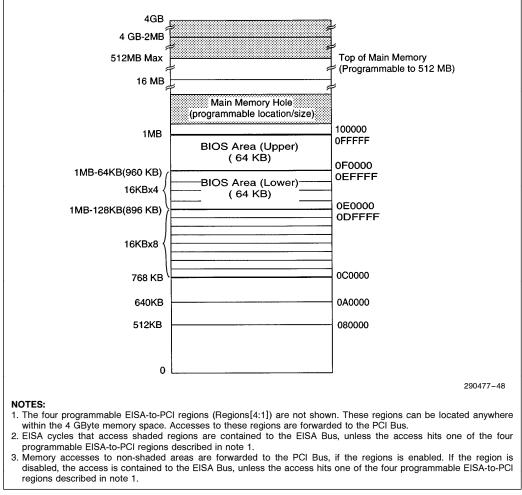

EISA/ISA masters and DMA can access PCI memory or I/O. The PCEB only forwards EISA cycles to the PCI Bus if the address of the transfer matches one of the address ranges programmed into the PCEB for EISA-to-PCI positive decode. This includes the main memory segments used for generating MEMCS# from the EISA Bus, one of the four programmable memory regions, or one of the four programmable I/O regions. For EISA-initiated accesses to the PCI Bus, the PCEB is a slave on the EISA Bus. I/O accesses are always non-buffered and memory accesses can be either non-buffered or buffered via the Line Buffers. For buffered accesses, burst cycles are supported.

During PCI-initiated cycles to the EISA Bus, the PCEB is an EISA master. Single cycle transfers are used for I/ O and memory read/write cycles from PCI to EISA.

#### PCI/EISA Address Decoding

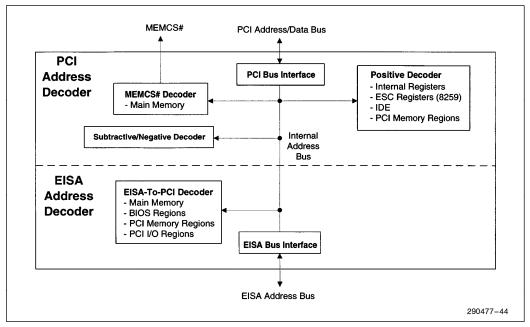

The PCEB contains two address decoders—one to decode PCI-initiated cycles and the other to decode EISAinitiated cycles. The two decoders permit the PCI and EISA Buses to operate concurrently.

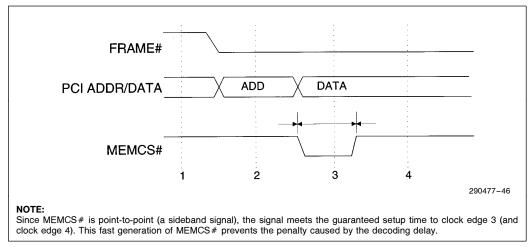

The PCEB can also be programmed to provide main memory address decoding on behalf of the Host/PCI bridge. When programmed, the PCEB monitors the PCI and EISA bus cycle addresses, and generates a memory chip select signal (MEMCS#) indicating that the current cycle is targeted to main memory residing behind the Host/PCI bridge. Programmable features include, read/write attributes for specific memory segments and the enabling/disabling of a memory hole. If not used, the MEMCS# feature can be disabled.

In addition to the main memory address decoding, there are four programmable memory regions and four programmable I/O regions for EISA-initiated cycles. EISA/ISA master or DMA accesses to one of these regions are forwarded to the PCI Bus.

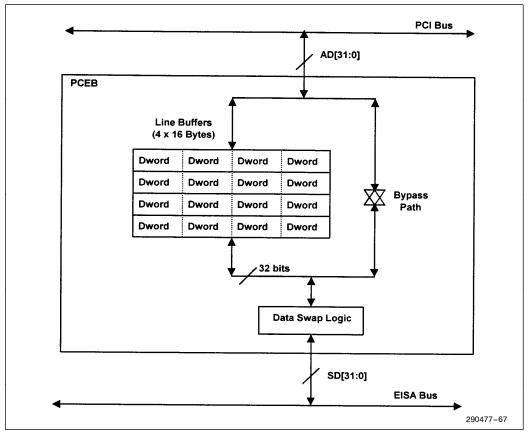

#### Data Buffering

The PCEB contains four 16-byte wide Line Buffers for EISA-initiated cycles to the PCI Bus. The Line Buffers permit prefetching of read data from PCI memory and posting of data being written to PCI memory.

By using burst transactions to fill or flush these buffers, when appropriate, the PCEB maximizes bus efficiency. For example, an EISA device could fill a Line Buffer with byte, word, or Dword transfers and the PCEB would use a PCI burst cycle to flush the filled line to PCI memory.

#### **BIOS Timer**

The PCEB has a 16-bit BIOS Timer. The timer can be used by BIOS software to implement timing loops. The timer count rate is derived from the EISA clock (BCLK) and has an accuracy of  $\pm 1 \ \mu$ s.

# 1.2 ESC Overview

The PCEB and ESC form a PCI-EISA bridge. The PCEB/ESC interface provides the inter-chip communications between these two devices. The major functions provided by the ESC are described in this section.

### **EISA Controller**

The ESC incorporates a 32-bit master and an 8-bit slave. The ESC directly drives eight EISA slots without external data or address buffering. EISA system clock (BCLK) generation is integrated by dividing the PCI clock (divide by 3 or divide by 4) and wait state generation is provided. The AENx and MACKx signals provide a direct interface to four EISA slots and supports eight EISA slots with encoded AENx and MACKx signals.

The ESC contains an 8-bit data bus (lower 8 bits of the EISA data bus) that is used to program the ESC's internal registers. Note that for transfers between the PCI and EISA Buses, the PCEB provides the data path. Thus, the ESC does not require a full 32-bit data bus. A full 32-bit address bus is provided and is used during refresh cycles and for DMA operations.

The ESC performs cycle translation between the EISA Bus and ISA Bus. For mis-matched master/slave combinations, the ESC controls the data swap buffers that are located in the PCEB. This control is provided through the PCEB/ESC interface.

#### **DMA Controller**

The ESC incorporates the functionality of two 82C37 DMA controllers with seven independently programmable channels. Each channel can be programmed for 8- or 16-bit DMA device size, and ISA-compatible, type "A", type "B", or type "C" timings. Full 32-bit addressing is provided. The DMA controller also generates refresh cycles.

The DMA controller supports an enhanced feature called scatter/gather. This feature provides the capability of transferring multiple buffers between memory and I/O without CPU intervention. In scatter/gather mode, the DMA can read the memory address and word count from an array of buffer descriptors, located in main memory, called the scatter/gather descriptor (SGD) table. This allows the DMA controller to sustain DMA transfers until all of the buffers in the SGD table are handled.

### Interrupt Controller

The ESC contains an EISA compatible interrupt controller that incorporates the functionality of two 82C59 Interrupt Controllers. The two interrupt controllers are cascaded providing 14 external and two internal interrupts.

#### Advanced Programmable Interrupt Controller (APIC)

In addition to the standard EISA compatible interrupt controller described above, the ESC incorporates the Advanced Programmable Interrupt Controller (APIC). While the standard interrupt controller is intended for use in a uni-processor system, APIC can be used in either a uni-processor or multi-processor system. APIC provides multi-processor interrupt management and incorporates both static and dynamic symmetric interrupt distribution across all processors. In systems with multiple I/O subsystems, each subsystem can have its own set of interrupts.

### Timer/Counter

The ESC provides two 82C54 compatible timers (Timer 1 and Timer 2). The counters in Timer 1 support the system timer interrupt (IRQ0#), refresh request, and a speaker tone output (SPKR). The counters in Timer 2 support fail-safe time-out functions and the CPU speed control.

### **Integrated Support Logic**

To minimize the chip count for board designs, the ESC incorporates a number of extended features. The ESC provides support for ALTA20 (Fast A20GATE) and ALTRST with I/O Port 92h. The ESC generates the control signals for SA address buffers and X-Bus buffer. The ESC also provides chip selects for BIOS, the keyboard controller, the floppy disk controller, and three general purpose devices. Support for generating chip selects with an external decoder is provided for IDE, a parallel port, and a serial port. The ESC provides support for a PC/AT compatible coprocessor interface and IRQ13 generation.

#### Power Management

Extensive power management capability permits a system to operate in a low power state without being powered down. Once in the low power state (called "Fast Off" state), the computer appears to be off. For example, the SMM code could turn off the CRT, line printer, hard disk drive's spindle motor, and fans. In addition, the CPU's clock can be governed. To the user, the machine appears to be in the off state. However, the system is actually in an extremely low power state that still permits the CPU to function and maintain communication connections normally associated with today's desktops (e.g., LAN, Modem, or FAX). Programmable options provide power management flexibility. For example, various system events can be programmed to place the system in the low power state or break events can be programmed to wake the system up.

### 2.0 SIGNAL DESCRIPTION

This section provides a detailed description of each signal. The signals are arranged in functional groups according to their associated interface.

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used extensively. This is done to avoid confusion when working with a mixture of "active-low" and "active-high" signals. The term **assert**, or **assertion** indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term **negate**, or **negation** indicates that a signal is inactive.

The following notations are used to describe the signal type.

- in Input is a standard input-only signal

- out Totem Pole output is a standard active driver

- o/d Open Drain input/output

- t/s Tri-State is a bi-directional, tri-state input/output pin

- s/t/s Sustained Tri-State is an active low tri-state signal owned and driven by one and only one agent at a time. The agent that drives a s/t/s pin low must drive it high for at least one clock before letting it float. A new agent can not start driving a s/t/s signal any sooner than one clock after the previous owner tri-states it. An external pull-up is required to sustain the inactive state until another agent drives it and must be provided by the central resource.

# int<sub>el</sub>.

# 2.1 PCI Bus Interface Signals

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCICLK   | in   | <b>PCI CLOCK:</b> PCICLK provides timing for all transactions on the PCI Bus. All other PCI signals are sampled on the rising edge of PCICLK and all timing parameters are defined with respect to this edge. Frequencies supported by the PCEB range from 25 to 33 MHz.                                                                                                                                                                                                                                                                                                             |

| PCIRST # | in   | <b>PCI RESET:</b> PCIRST # forces the PCEB into a known state. All t/s and s/t/s signals are forced to a high impedance state, and the s/o/d signals are allowed to float high. The PCEB negates all GNT # lines to the PCI Bus and the PCEB negates its internal request. The PCEB drives AD[31:0], C/BE[3:0] #, and PAR during reset to keep these signals from floating (depending on the state of CPUREQ# and REQ1#—as described in the following paragraph).                                                                                                                    |

|          |      | As long as PCIRST# is asserted, the PCEB drives the AD[31:0] signals to keep them from floating. Note that CPUREQ# must be sampled high when PCIRST# is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          |      | All PCEB registers are set to their default values. PCIRST# may be asynchronous to PCICLK when asserted or negated. Although asynchronous, the negation of PCIRST# must be a clean, bounce-free edge. PCIRST# must be asserted for a minimum 1 $\mu$ s, and PCICLK must be active during the last 100 $\mu$ s of the PCIRST# pulse.                                                                                                                                                                                                                                                  |

| AD[31:0] | t/s  | <b>ADDRESS AND DATA:</b> AD[31:0] is a multiplexed address and data bus. During the first clock of a transaction, AD[31:0] contain a physical address. During subsequent clocks, AD[31:0] contain data.                                                                                                                                                                                                                                                                                                                                                                              |

|          |      | A PCEB bus transaction consists of an address phase followed by one or more data phases. Little-endian byte ordering is used. AD[7:0] define the least significant byte (LSB) and AD[31:24] the most significant byte (MSB). The information contained in the two low order address bits varies by address space. In the I/O address space, AD[1:0] are used to provide full byte address. In the memory and configuration address space, AD[1:0] are driven "00" during the address phase. The other three encodings are reserved. See Section 5.0, PCI Interface for more details. |

|          |      | When the PCEB is a target, AD[31:0] are inputs during the address phase of a transaction. During the following data phase(s), the PCEB may be asked to supply data on AD[31:0] as for a PCI read, or accept data as for a PCI write. As an Initiator, the PCEB drives a valid address on AD[31:0] (with exceptions related to AD[1:0]) during the address phase, and drives write or latches read data on AD[31:0] during the data phase.                                                                                                                                            |

|          |      | When PCIRST # is asserted, the PCEB drives the AD[31:0] signals to keep them from floating. In addition, the PCEB acts as the central resource responsible for driving the AD[31:0] signals when no device owns the PCI Bus and the bus is idle.                                                                                                                                                                                                                                                                                                                                     |

Advance information

# int<sub>el</sub>.

| Pin Name   | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C/BE[3:0]# | t/s   | <b>BUS COMMAND AND BYTE ENABLES:</b> The command and byte enable signals are multiplexed on the same PCI pins. During the address phase of a transaction, C/BE[3:0] # define the bus command for bus command definitions. During the data phase, C/BE[3:0] # are used as Byte Enables. The Byte Enables determine which byte lanes carry meaningful data. C/BE[0] # applies to byte 0 and C/BE[3] # to byte 3. C/BE[3:0] # are not used for address decoding.                                                                                                                             |

|            |       | The PCEB drives C/BE[3:0] # as an initiator of a PCI Bus cycle and monitors C/BE[3:0] # as a target.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            |       | When PCIRST# is asserted, the PCEB drives C/BE[3:0] # to keep them from floating. In addition, the PCEB acts as the central resource responsible for driving the C/BE[3:0] # signals when no device owns the PCI Bus and the bus is idle                                                                                                                                                                                                                                                                                                                                                  |

| FRAME#     | s/t/s | <b>FRAME:</b> FRAME # is driven by the current initiator to indicate the beginning and duration of an access. FRAME # is asserted to indicate that a bus transaction is beginning. During a transaction, data transfers continue while FRAME # is asserted. When FRAME # is negated, the transaction is in the final data phase. FRAME # is an input when the PCEB is the target. FRAME # is an output when the PCEB is the initiator. During reset, this signal is tri-stated.                                                                                                           |

| TRDY#      | s/t/s | <b>TARGET READY:</b> TRDY #, as an output, indicates the target's ability to complete the current data phase of the transaction. TRDY # is used in conjunction with IRDY #. A data phase is completed on any clock that both TRDY # and IRDY # are sampled asserted. When PCEB is the target during a read cycle, TRDY # indicates that the PCEB has valid data present on AD[31:0]. During a write, it indicates that the PCEB, as a target, is prepared to latch data. TRDY # is an input to the PCEB when the PCEB is the initiator. During reset, this signal is tri-stated.          |

| IRDY#      | s/t/s | <b>INITIATOR READY:</b> IRDY #, as an output, indicates the initiator's ability to complete the current data phase of the transaction. IRDY # is used in conjunction with TRDY #. A data phase is completed on any clock that both IRDY # and TRDY # are sampled asserted. When PCEB is the initiator of a write cycle, IRDY # indicates that the PCEB has valid data present on AD[31:0]. During a read, it indicates the PCEB is prepared to latch data. IRDY # is an input to the PCEB when the PCEB is the target. During reset, this signal is tri-stated.                           |

| STOP#      | s/t/s | <b>STOP:</b> As a target, the PCEB asserts STOP# to request that the master stop the current transaction. When the PCEB is an initiator, STOP# is an input. As an initiator, the PCEB stops the current transaction when STOP# is asserted. Different semantics of the STOP# signal are defined in the context of other handshake signals (TRDY# and DEVSEL#). During reset, this signal is tri-stated.                                                                                                                                                                                   |

| PLOCK#     | s/t/s | <b>PCI LOCK:</b> PLOCK# indicates an atomic operation that may require multiple transactions to complete. PLOCK# is an input when PCEB is the target and output when PCEB is the initiator. When PLOCK# is sampled negated during the address phase of a transaction, a PCI agent acting as a target will consider itself a locked resource until it samples PLOCK# and FRAME# negated. When other masters attempt accesses to the PCEB (practically to the EISA subsystem) while the PCEB is locked, the PCEB responds with a retry termination. During reset, this signal is tristated. |

# intel

| Pin Name | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDSEL    | in    | <b>INITIALIZATION DEVICE SELECT:</b> IDSEL is used as a chip select during configuration read and write transactions. The PCEB samples IDSEL during the address phase of a transaction. If the PCEB samples IDSEL asserted during a configuration read or write, the PCEB responds by asserting DEVSEL# on the next cycle.                                                                                                                                                                                                                                                                            |

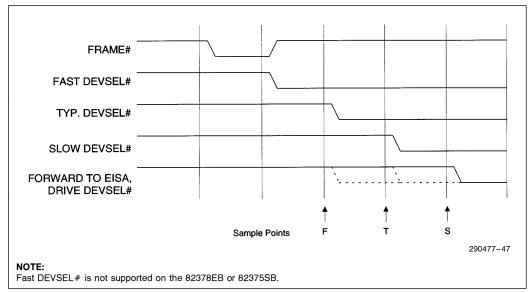

| DEVSEL#  | s/t/s | <b>DEVICE SELECT:</b> The PCEB asserts DEVSEL# to claim a PCI transaction as a result of positive or subtractive decode. As an output, the PCEB asserts DEVSEL# when it samples IDSEL asserted during configuration cycles to PCEB configuration registers.                                                                                                                                                                                                                                                                                                                                           |

|          |       | As an input, DEVSEL # indicates the response to a PCEB-initiated transaction. The PCEB, when not a master, samples this signal for all PCI transactions to decide whether to subtractively decode the cycle (except for configuration and special cycles). During reset, this signal is tri-stated.                                                                                                                                                                                                                                                                                                   |

| PAR      | t/s   | <b>PARITY:</b> PAR is even parity across AD[31:0] and C/BE[3:0] #. When acting as a master, the PCEB drives PAR during the address and write data phases. As a target, the PCEB drives PAR during read data phases.                                                                                                                                                                                                                                                                                                                                                                                   |

|          |       | When PCIRST# is asserted, the PCEB drives the PAR signal to keep it from floating.<br>The PCEB acts as the central resource responsible for driving the PAR signal when no<br>other device is granted the PCI Bus and the bus is idle.                                                                                                                                                                                                                                                                                                                                                                |

|          |       | Note that the driving and tri-stating of the PAR signal is always one clock delayed from the corresponding driving and tri-stating of the AD[31:0] and C/BE[3:0] # signals.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PERR #   | s/t/s | <b>PARITY ERROR:</b> PERR # reports data parity errors on all transactions, except special cycles. This signal can only be asserted (by the agent receiving data) two clocks following the data (which is one clock following the PAR signal that covered the data). The duration of PERR # is one clock for each data phase that a data parity error is detected. (If multiple data errors occur during a single transaction the PERR # signal is asserted for more than a single clock.) PERR # must be driven high for one clock before being tri-stated. During reset, this signal is tri-stated. |

Advance information

# 2.2 PCI Arbiter Signals

| Pin Name   | Туре |                                                   |                                                                    | Description                                                                                                                                                                                                                                                                     |

|------------|------|---------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPUREQ#    | in   | the PCI Bus. I<br>PCIRST # is a                   | During PCIRST<br>Isserted (and C                                   | asserted indicates that the Host CPU requests use of<br>#, this signal must be sampled high by the PCEB. When<br>CPUREQ# is sampled high), the PCEB drives the AD,<br>keep them from floating.                                                                                  |

| REQ[3:0] # | in   | REQUEST: A<br>PCI Bus.                            | bus master as                                                      | serts the corresponding request signal to request the                                                                                                                                                                                                                           |

| CPUGNT#    | out  |                                                   |                                                                    | serts CPUGNT# to indicate that the CPU master (Host<br>e PCI Bus. During PCI reset, CPUGNT# is tri-stated.                                                                                                                                                                      |

| GNT[3:0]#  | out  |                                                   | g PCI master h                                                     | one of the GNT[3:0] signals to indicate that the<br>as been granted the PCI Bus. During PCI reset, these                                                                                                                                                                        |

| MEMREQ#    | out  | Mode, MEMR<br>The PCEB as<br>requires owne        | EQ# is asserte<br>serts this signa<br>ership of main r<br>MEMREQ#. | PCEB is configured in Guaranteed Access Time (GAT)<br>ed when an EISA device or DMA requests the EISA Bus.<br>I (along with FLSHREQ#) to indicate that the PCEB<br>nemory. The PCEB asserts FLSHREQ# concurrently<br>This signal is synchronous to the PCI clock. During reset, |

|            |      | FLSHREQ#                                          | MEMREQ#                                                            | Meaning                                                                                                                                                                                                                                                                         |

|            |      | 1                                                 | 1                                                                  | Idle                                                                                                                                                                                                                                                                            |

|            |      | 0                                                 | 1                                                                  | Flush buffers pointing towards PCI                                                                                                                                                                                                                                              |

|            |      |                                                   |                                                                    | to avoid ISA deadlock                                                                                                                                                                                                                                                           |

|            |      | 1                                                 | 0                                                                  | GAT enabled or disabled: For buffer                                                                                                                                                                                                                                             |

|            |      |                                                   |                                                                    | coherency in APIC systems, the                                                                                                                                                                                                                                                  |

|            |      |                                                   |                                                                    | buffers pointing to main memory                                                                                                                                                                                                                                                 |

|            |      |                                                   |                                                                    | must be flushed and disabled for the                                                                                                                                                                                                                                            |

|            |      |                                                   |                                                                    | duration of assertion.                                                                                                                                                                                                                                                          |

|            |      | 0                                                 | 0                                                                  | GAT mode: Guarantee PCI Bus                                                                                                                                                                                                                                                     |

|            |      |                                                   |                                                                    | immediate access to main memory                                                                                                                                                                                                                                                 |

|            |      |                                                   |                                                                    | (this may or may not require the                                                                                                                                                                                                                                                |

|            |      |                                                   |                                                                    | PCI-to-main memory buffers to be                                                                                                                                                                                                                                                |

|            |      |                                                   |                                                                    | flushed first, depending on the<br>number of buffers).                                                                                                                                                                                                                          |

| FLSHREQ#   | out  | system's post<br>before grantir<br>related buffer | ed write buffer<br>g the EISA Bu<br>flush requests                 | EQ # is asserted by the PCEB to command all of the s pointing towards PCI to be flushed. This is required s to an EISA master or the DMA. Note that, for APIC, this signal is negated. This signal is synchronous to the signal is driven high.                                 |

# int<sub>el</sub>.

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                |

|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMACK#  | in   | <b>MEMORY ACKNOWLEDGE:</b> MEMACK # is the response handshake that indicates to the PCEB that the function requested over the MEMREQ # and/or FLSHREQ # signals has been completed.                                                                                                                                        |

|          |      | If the PCEB is configured for Guaranteed Access Time Mode through the Arbiter<br>Control Register, and both MEMREQ# and FLSHREQ# are asserted, the assertion<br>of MEMACK# indicates to the PCEB that ownership of main memory has been<br>granted and that all system buffers have been flushed and temporarily disabled. |

|          |      | If MEMACK # is asserted in response to assertion of MEMREQ # (GAT either<br>enabled or disabled), it indicates that the system's buffers pointing towards the main<br>memory are flushed and temporarily disabled so that APIC can proceed with the<br>interrupt message sequence.                                         |

|          |      | If FLSHREQ # is asserted and MEMREQ # is not asserted (with GAT mode being either enabled or disabled), the assertion of MEMACK # indicates that the system's posted write buffers pointing towards PCI are flushed and temporarily disabled, and the EISA Bus can be granted to an EISA master or DMA.                    |

|          |      | This signal is synchronous to the PCI clock.                                                                                                                                                                                                                                                                               |

# 2.3 Address Decoder Signals

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                     |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMCS #  | out  | <b>MEMORY CHIP SELECT:</b> MEMCS# is a programmable address decode signal provided to a Host CPU bridge. A Host bridge can use MEMCS# to forward a PCI cycle to the main memory behind the bridge. MEMCS# is asserted one PCI clock after FRAME# is sampled asserted (address phase) and is valid for one clock cycle before being negated. MEMCS# is driven high during reset. |

| PIODEC#  | in   | <b>PCI I/O SPACE DECODER:</b> PIODEC # can be used to provide arbitrarily complex EISA-to-PCI I/O address space mapping. This signal can be connected to the decode select output of an external I/O address decoder. When PIODEC # is asserted during an EISA I/O cycle, that cycle is forwarded to the PCI Bus.                                                               |

|          |      | Note that an external pull-up resistor is required if this input signal is not used (i.e., not driven by the external logic).                                                                                                                                                                                                                                                   |

# 2.4 EISA Interface Signals

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                         |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCLK     | in   | <b>BUS CLOCK:</b> BCLK is the system clock used to synchronize events on the EISA Bus.<br>The ESC device generates BCLK (BCLKOUT), which is a divided down clock from a<br>PCICLK. BCLK runs at a frequency that is dependent on PCICLK and a selected<br>division factor (within the ESC). For example, a 25 MHz PCICLK and a division factor of<br>3 results in an 8.33 MHz BCLK. |

| START#   | t/s  | <b>START:</b> START# provides timing control at the start of the cycle and remains asserted for one BCLK period.                                                                                                                                                                                                                                                                    |

|          |      | When the PCEB is an EISA master, START# is an output signal. START# is asserted after LA[31:24] #, LA[23:2] and M/IO# become valid. START# is negated on the rising edge of the BCLK, one BCLK after it was asserted. The trailing edge of START# is always delayed from the rising edge of BCLK.                                                                                   |

|          |      | When the PCEB is an EISA master, for cycles to a mismatched slave (see note at the end of this section), START# becomes an input signal at the end of the first START# phase and remains an input until the negation of the last CMD#. The ESC gains the control of the transfer and generates START#.                                                                              |

|          |      | When the PCEB is an EISA slave, START# is an input signal. It is sampled on the rising edge of BCLK.                                                                                                                                                                                                                                                                                |

|          |      | Upon PCIRST#, this signal is tri-stated and placed in output mode.                                                                                                                                                                                                                                                                                                                  |

| CMD#     | in   | <b>COMMAND:</b> CMD# provides timing control within the cycle. In all cases, CMD# is an input to the PCEB from the ESC. CMD# is asserted from the rising edge of BCLK, simultaneously with the negation of START#, and remains asserted until the end of the cycle.                                                                                                                 |

| M/IO#    | t/s  | <b>MEMORY OR I/O:</b> $M/IO #$ identifies the current cycle as a memory or an I/O cycle.<br>M/IO# is pipelined from one cycle to the next and must be latched by the slave.<br>M/IO # = 1 indicates a memory cycle and $M/IO # = 0$ indicates an I/O cycle.                                                                                                                         |

|          |      | When the PCEB is an EISA master, the M/IO# is an output signal. When the PCEB is an EISA slave, M/IO# is an input signal. The PCEB responds as an EISA slave for both memory and I/O cycles. Upon PCIRST#, this signal is tri-stated and is placed in output mode.                                                                                                                  |

| W/R#     | t/s  | <b>WRITE OR READ:</b> W/R# identifies the cycle as a write or a read cycle. The W/R# signal is pipelined from one cycle to the next and must be latched by the slave. W/R# $=$ 1 indicates a write cycle and W/R# $=$ 0 indicates a read cycle.                                                                                                                                     |

|          |      | When the PCEB is an EISA master, $W/R \#$ is an output signal. When the PCEB is an EISA slave, $W/R \#$ is an input signal. Upon PCIRST $\#$ , this signal is tri-stated and placed in output mode.                                                                                                                                                                                 |

Advance information

# intel

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| EXRDY    | od   | <b>EISA READY:</b> EXRDY is used by EISA I/O and memory slaves to request wait states during a cycle. Each wait state is a BCLK period.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|          |      | The PCEB, as an EISA master or slave, samples EXRDY. As an input, the EXRDY is<br>sampled on the falling edge of BCLK after the CMD# has been asserted, and if<br>inactive, each falling edge thereafter.                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|          |      | When PCEB is an EISA slave, it may drive EXRDY low to introduce wait states.<br>During reset, this signal is not driven.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| EX32#    | od   | <b>EISA 32 BIT:</b> EX32# is used by the EISA slaves to indicate support of 32 bit transfers. When the PCEB is an EISA master, it samples EX32# on the same rising edge of BCLK that START# is negated.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|          |      | During mismatched cycles (see note at the end of this section), EX32# (and EX16#) is used to transfer the control back to the PCEB. EX32# (along with EX16#) is asserted by the ESC on the falling edge of BCLK before the rising edge of the BCLK when the last CMD# is negated. This indicates that the cycle control is transferred back to the PCEB.                                                                                                                                                                                                                               |  |  |

|          |      | As an EISA slave, the PCEB always drives EX32# to indicate 32 bit support for EISA cycles. During reset, this signal is not driven.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| EX16#    | in   | <b>EISA 16 BIT:</b> EX16# is used by the EISA slaves to indicate their support of 16 bit transfers. As an EISA master, the PCEB samples EX16# on the same rising edge of BCLK that START# is negated.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|          |      | During mismatched cycles (see note at the end of this section), EX16# (and EX32#) is used to transfer the control back to the PCEB. EX16# (along with EX32#) is asserted by the ESC on the falling edge of the BCLK before the rising edge of the BCLK when the last CMD# is negated. This indicates that the cycle control is transferred back to the PCEB.                                                                                                                                                                                                                           |  |  |

|          |      | As an EISA slave, the PCEB never asserts EX16#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| MSBURST# | t/s  | <b>MASTER BURST:</b> MSBURST # is an output when the PCEB is an EISA master and an input when the PCEB is a slave.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|          |      | As a master, the PCEB asserts MSBURST# to indicate to the slave that the next cycle is a burst cycle. If the PCEB samples SLBURST# asserted on the rising edge of BCLK after START# is asserted, the PCEB asserts MSBURST# on the next BCLK edge and proceeds with the burst cycle.                                                                                                                                                                                                                                                                                                    |  |  |

|          |      | As a slave, the PCEB monitors this signal in response to the PCEB asserting SLBURST#. The EISA master asserts MSBURST# to the PCEB to indicate that the next cycle is a burst cycle. As a slave, the PCEB samples MSBURST# on the rising edge of BCLK after the rising edge of BCLK that CMD# is asserted by the ESC. MSBURST# is sampled on all subsequent rising edges of BCLK until the signal is sampled negated. The burst cycle is terminated on the rising edge of BCLK when MSBURST# is sampled negated, unless EXRDY is sampled negated on the previous falling edge of BCLK. |  |  |

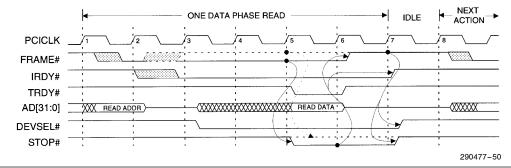

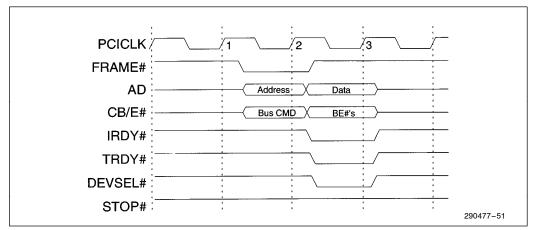

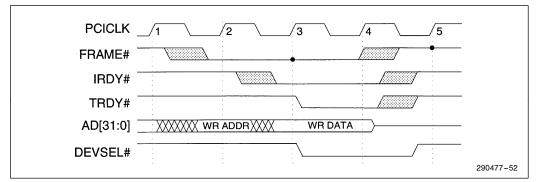

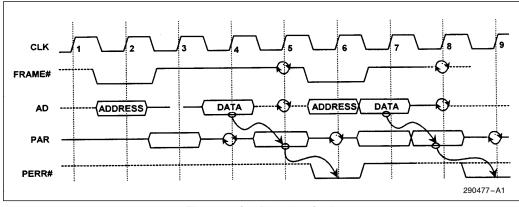

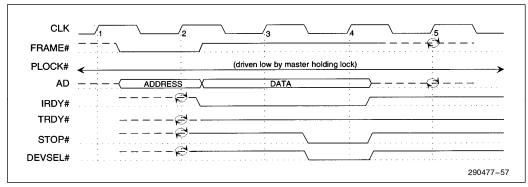

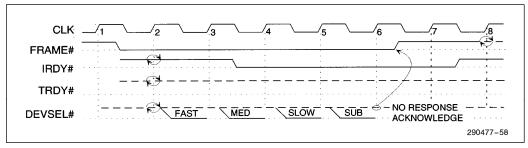

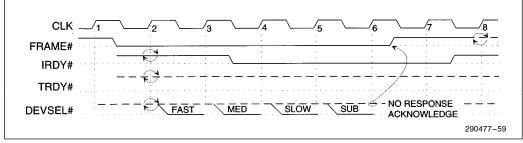

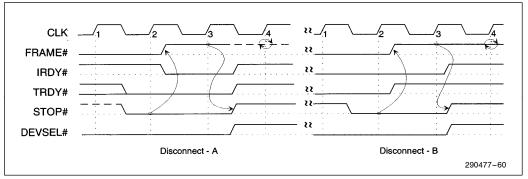

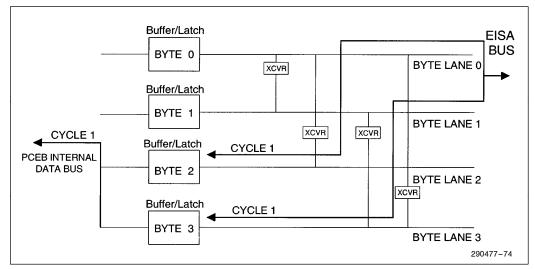

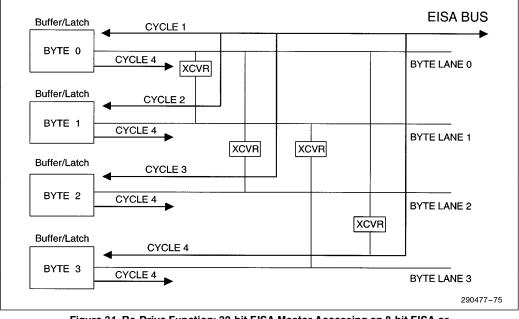

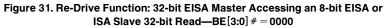

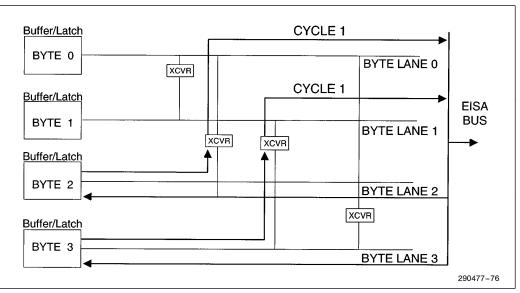

| Pin Name                | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                            |